## **FUZZY LOGIC NEURAL PROCESSOR**

J.B. Kiszka\*, M.M. Gupta\*\*

\* Electrical Engineering Lakehead University Thunder Bay, Ontario P7B 5E1 Canada

\*\* College of Engineering University of Saskatchewan Saskatoon, Sask. S7N 0W0 Canada

Abstract:

An architecture of fuzzy logic neural processor is discussed. General structure of fuzzy logic neural processor based on t-norm and t-conorm is proposed.

## 1. Introduction.

An intention of this paper is to outline of a highly parallel architecture of a fuzzy logic dynamic neural processor. Our discussion is based on a theory of fuzzy logic neurons sketched in [1], and [2].

# 2. Architecture of fuzzy logic neural processor.

In [1] the dynamic behavior of the neuron has been shaped as follows

$$\begin{cases} X_{n+1} = X_n \circ R_1 \Delta U_n^1 \circ R_2 \Delta U_n^2 \circ R_3 \\ Y_n = X_n \circ R_4 \Delta U_n^1 \circ R_5 \Delta U_n^2 \circ R_6 \end{cases}$$

(1)

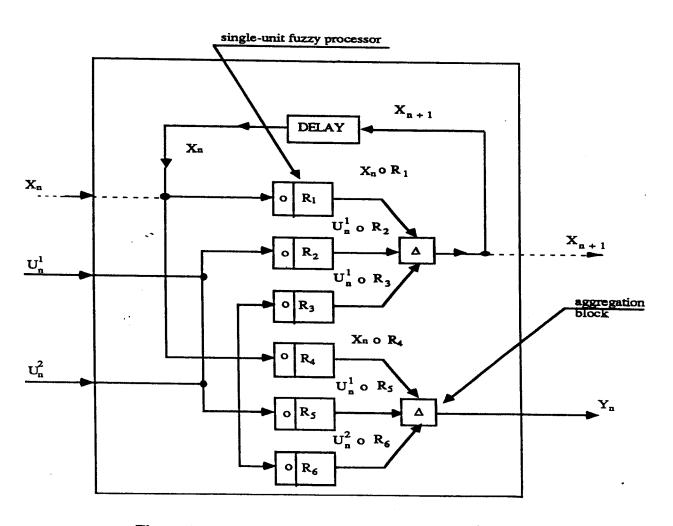

An architecture of fuzzy logic neural processor is depicted in Figure 1.

Figure 1. Architecture of dynamic fuzzy neuron.

It is interesting to note that the fuzzy neuron consists of six single-unit fuzzy processors R<sub>1</sub>, R<sub>2</sub>,

$R_3$ ,  $R_4$ ,  $R_5$ , and  $R_6$ ; two contribution blocks  $\Delta$ , and delay block.

One should note that the above configuration processes fuzzy information dynamically in parallel mode using only three basic blocks.

It is worth to investigate a nature of a single-unit fuzzy neuron processor. Viewing into a nature of a neuron it is worth to recall that a highly nonlinear property with a flexible saturation must be considered. Thinkging of the above paradigm and Equation (1) we propose the following model of a single-unit fuzzy neuron processor  $R_1$ .

$$X_{n+1} = X_n$$

o  $R_1$ ,  $n = 0, 1, 2, 3, ...$

where

$$R_{1} = \bigwedge_{i=1}^{I} \begin{cases} 1, X_{n(i)} \leq X_{n+1(i)} \\ X_{n(i)}, X_{n(i)} > X_{n+1(i)} \end{cases}$$

therefore

$$X_{n+1} = \bigvee_{X} \left[ X_{n} \wedge \bigwedge_{i=1}^{I} \left\{ \begin{array}{c} 1, \ X_{n(i)} \leq X_{n+1(i)} \\ \\ X_{n(i)}, X_{n(i)} > X_{n+1(i)} \end{array} \right] \right]$$

and finally

$$X_{n+1} = \bigvee_{X} \left[ \bigwedge_{i=1}^{I} \left\{ \begin{array}{l} 1, X_{n(i)} \leq X_{n+1(i)} \\ X_{n} \wedge X_{n(i)}, X_{n(i)} > X_{n+1(i)} \end{array} \right] \right]$$

(2)

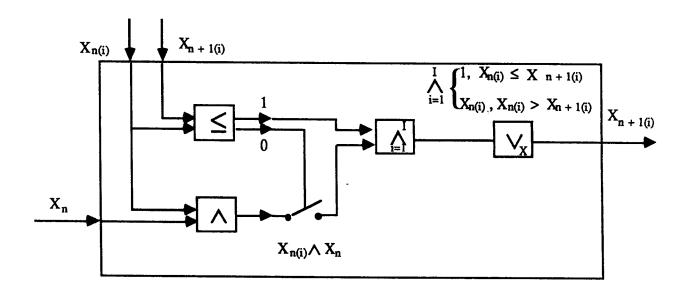

A block diagram architecture in terms of mathematical operations of the single-unit fuzzy neuron processor is depicted in Figure 2.

It consists of a logic gate "equal or less than  $\leq$ ", a "min-aggregation gate  $\bigwedge_i$ ", and a "sup-gate  $\bigvee_X$ ".

It is worth to stress that a basic building block of any dynamic fuzzy neuron is expressed by Equation (2) and dipicted in Figure 2.

It remains to say that the single-unit fuzzy neuron processor exhibits a highly parallel architecture.

Figure 2. A block-diagram architecture of a single-unit fuzzy neruon processor  $R_1$ .

#### 3. Generalized structure of fuzzy logic processor.

In general any fuzzy static neuron with 2 inputs and 1 output can be formulized by the following

$$Y = X_{1} * \left\{ \bigodot_{i=1}^{I} \left[ X_{1(i)} \bigodot_{i} Y_{(i)} \right] \right\} \Delta$$

$$\Delta X_{2} * \left\{ \bigodot_{i=1}^{I} \left[ X_{2(i)} \bigodot_{i} Y_{(i)} \right] \right\}$$

(3)

where \* denotes a generalized inference operator, (a) is a generalized aggregation operator, (b) is a generalized implication operator, and  $\Delta$  denotes a generalized contribution operator.

Equation (3) can be extended to M-inputs fuzzy neuron as follows

$$Y = \bigwedge_{k=1}^{M} \left\{ X_{K} * \left[ \underbrace{a}_{i=1}^{I} \left[ X_{K(i)} \stackrel{b}{\longrightarrow} Y_{(i)} \right] \right] \right\}$$

(4)

where k = 1, 2, 3, ..., M is the number of inputs.

Triangular norms and their dual triangular conorms could be used to generate the aggregation operator  $\Delta$ , the composition operator \*, and the contribution operators  $\overline{a}$ .

Consequantly in terms of t-norm and t-conorm, the M-input fuzzy neuron (4) may be expressed as

$$Y = \mathbf{T}_{K=1}^{M} \left\{ \mathbf{S}_{X} \left[ X_{K} \mathbf{T} \left[ \mathbf{S}_{i=1}^{T} \left( X_{K(i)} \mathbf{b} Y_{(i)} \right) \right] \right] \right\}$$

(5)

where T stands for t-norm, and S denotes t-conorm.

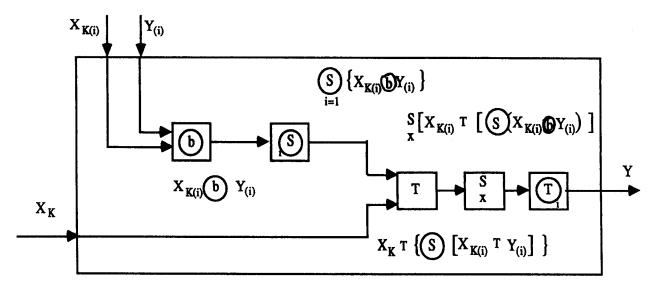

General architecture of M-input fuzzy neuron in terms of t-norm, t-conorm and implication operator is depicted in Figure 3.

The generalized architecture of the fuzzy neuron consists of : an implication gate b, a t-norm aggregation gate s, and t-conorm gate T, an inf-conorm gate s and a t-conorm gate T.

Figure 3. Generalized architecture of M-input fuzzy neuron.

### 4. Summary.

An architecture of fuzzy logic neural processor has been proposed. This investigation may have an impact on VLSI implementation of fuzzy logic neural systems.

#### References.

- [1] J. Kiszka, M.M. Gupta, Fuzzy logic model of single neuron, BUSEFAL, 1989.

- [2] J. Kiszka, M. Gupta, Fuzzy logic neural network, BUSEFAL, 1989.